半導體產業研究:

到底什麼是半導體7奈米製程?

一般人可能會以為做半導體晶片就跟做蛋糕一樣,只要一層一層疊上去就會成功了,什麼7奈米,5奈米,3奈米,2奈米,反正都差不多,但是蛋糕做壞了還能吃,半導體做壞了,漏電太大的,耗電太多的,速度太慢的通通只能報廢,還不能當肥料。

40年前的半導體製造業時,聯電最先進的製程是6微米也就是6000奈米,後來艱辛的進入3微米也就是3000奈米,那時候的半導體製程工程師還可以用光學顯微鏡來檢查看看產品有沒有缺點?

因為光波波長大約400-800奈米,時隔40年,不知不覺中,半導體製程竟然已經從微米技術跨過1000奈米,進入130奈米,28奈米,14奈米,甚至近年來已經突破7奈米,過去認為近乎是人類製程技術的極限了,而且連5、3、2奈米的次世代製程圖也都有量產時程能攤開來談。

一顆矽原子直徑約0.1奈米,如果製程最薄處真的只有7奈米,就是說一片絕緣物是一片用70顆矽原子組成的氧化矽城牆,這麼薄的城牆,基本上是比1mm玻璃還透光的,重點是它還需具備絕緣的特性能夠不漏電,更有趣的是,依照量子力學,所有被關在牆內的電子,會有10%很自然地分佈在牆外,這種現象是量子力學的必然,與製程良窳無關,但是這種量子現象,從巨觀世界看,就是電晶體D-S間有10%漏電,也就是水龍頭永遠都關不緊的意思。

一顆MOS電晶體有三個極

D Drain 受極

S Source 源極

G Gate 閘極

閘極是用來控制從源極流往受極的電流,閘極G上的微小電壓可以控制D-S(源-受極)間的大電流,如同水龍頭控制水流,而能達成邏輯閘功能。

兩個邏輯閘結合可以成為一個記憶體,很多邏輯閘可以組成CPU DSP FPGA....等等.

7奈米世界的IC電路設計工程師,必需在忍受D-S間有漏電,如同使用一個明知道有漏水的水龍頭卻要設計出能持續維持乾燥的浴室一樣,這不是弄個乾溼分離就能解決,要用漏電的邏輯閘設計出可以用的邏輯電路。從此遊戲規則不再是以前絕對的1=100% 全通電 0=0% 完全斷電,而是類比型的1=70% 通電0=30%漏電。

這種情形對於過去習慣類比電路的骨灰級工程師或許覺得沒啥困難,因為古代的鍺電晶體Icbo漏電也是很嚴重,但是對生長於科技數位時代的小孩而言,這種狀況可能會瘋掉。(如果沒有網路和智慧型手機........那恐怕早已脫離能夠想像的年代)

Icbo 是古代鍺電晶體常見的熱漏電,與主題無關,在這裏暫不詳談。

假的7奈米製程

還好現在台積電號稱7奈米的製程,其實並沒有達到真正的7奈米技術,宣稱7奈米的電晶體,線寬其實是40奈米,閘極寬是20奈米,只有最細的D-S通道是寬7奈米,高52奈米、長60奈米,一顆MOS電晶體長寬高仍有40x60x100奈米大,這樣的尺寸離會產生量子隧道效應,造成嚴重漏電的7奈米其實還很遠,所以因量子力學造成的漏電只有1%,也就是1=99% 通電 0=1% 漏電,所以邏輯工程師還不需要太慌張。

2/3/5奈米

可是如果有一天半導體製程真得達到2奈米,實際絕緣牆是6奈米時,量子力學的物理現象就會很明顯,例如1=60% 通電 0=40% 漏電, 到了1奈米製程,絕緣牆只剩下3.5奈米時,1=55% 通電 0=45% 漏電,就會很好笑,這需要下一代的天才AI工程師,或是過去那些曾經用過高漏電鍺晶體並且能有效解決這種無法處理的正常物理現象的超級工程師來克服,才有可能解決這種嚴重量子漏電的問題。

希望那時候科技的進步已經能讓量子電腦實用化了,現在這種矽晶圓做的半導體已經如同真空管一樣通通變成骨董,放進博物館,不然只能希望人類能發現更新一代不具備這種物理現象的新材料。

******* 回到現實*********

如何建一條7奈米生產線

ㄧ條7奈米生產線,光是設備成本就要6000億台幣起跳,金額高到用國家力量支持都很吃力,台灣一年的稅收是20000億,只夠做3條7奈米生產線。

一家半導體公司每年的毛利如果沒有超過300億美金,是不可能每年投入200億美金資本支出的 ,一旦停止資本支出,就等著被別人超越。 毛利300億美金,等於1000億美金以上的營業額,即3兆台幣,比台灣一年的2兆元稅收還多 ,幾乎是20兆GDP的15%。

歐盟

即使傾全歐洲之力,也未必能支持一家長期虧錢的半導體公司,如果可以早就做了,如果做了就等著良率太低,生意不好,每年虧損100億美金,等於3000億台幣,歐洲各國財政早已捉襟見肘,一定不會持久,必定始亂終棄。

韓國

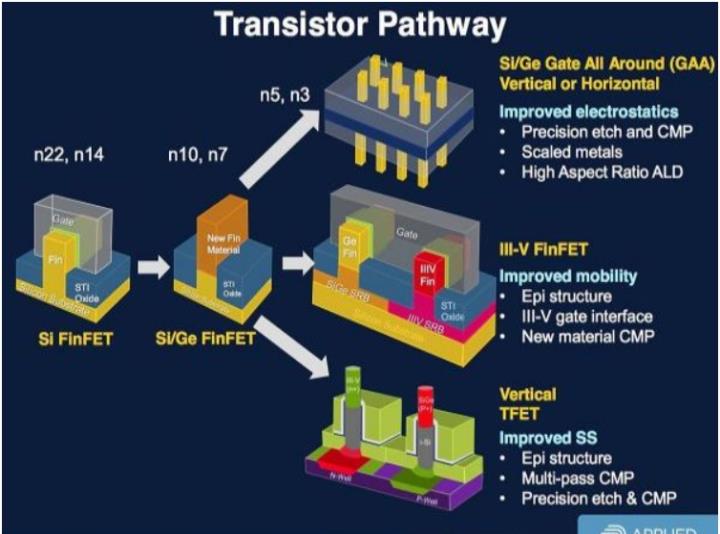

曾經的世界第一名,韓國三星的7奈米製程,即使還沒進入量子漏電世界,在巨觀世界的漏電問題就已無法解決,不用可靠的FIN,貪心直跳GAA 結構,良率會更搞不定,不但會繼續虧錢,而且會害死高通,高通貪便宜請三星代工,有點自取滅亡,這當然也讓聯發科有機會順利超車。

美國

世界第一強國美國的二號CPU DSP廠 AMD,早就已經徹底絕悟,放棄自己生產,全面請台積電代工,做出來的CPU立即將世界第一的Intel 打趴在地上,Intel的10奈米製程,至今良率上不來,一片12吋晶圓,製造成本美金15000元,如果良率高,做出200個良品,每顆成本美金75元,賣美金200元,賺得盆滿缽滿,每一個人都開法拉利。但是現在實際上做一片晶圓出來,測不到50個良品,等於一個CPU製造成本300元,賣一顆要倒賠100元,老本快要吃光了,Intel想要學AMD改請台積電代工,又拉不下臉,也怕一旦做了就永遠回不去了,真是進退失據,最近CEO又吹牛說要花200億美金,增加設備趕上台積電,但是金融業沒有一個看好他的策略,還沒募資,股價就通通投反對票。

美國軍方DARPA

雖然很著急,害怕最重要的飛彈用F-35 、F-22用的高速FPGA及其它IC都要靠台積電單一供應商,萬一台灣有事,例如大地震或阿共來犯就慘了,但是DARPA也不是白癡,不可能花300億美金再培養一個比 Intel 更糟的阿斗。

中國

全世界最有錢的中國,人才最優秀最奮鬥的民族,全世界最優秀最有效率的政府,從台灣挖走梁孟松、蔣尚義..等等諸多人才 。中國人雖然比台灣小孩還努力,還肯加班,但是缺乏最基本的紀律感與自律心,所以中國的半導體業努力20多年,20歲的中芯連14奈米的良率都還搞不定,根本無力分兵研發7奈米製程。中芯甚至連第一代ASML光刻機都還買不到,更不要說是ASML為台積電特製的光刻機,能使產能再提高50%的第三代超高功率光刻機。

中國的新創半導體公司,不幸都是一群諸如武漢弘芯之類的騙子在圈錢,在騙國家補助,說穿了大概絕大多數都是騙子在騙傻子。

汽車業全面缺半導體

中國、日本、韓國、美國、德國、法國、義大利的汽車業為了缺半導體而停止生產,傳統電子業也連帶遭殃,所以全世界各國都想恢復做半導體,過去20年被韓國跟台灣打趴的的日本半導體製造業現在也想重操舊業,不過他們的想法比較實際,都想學美國,邀請台積電去設廠,因為他們知道全世界只剩台灣人會願意去投資設廠,而且真的可以做好。

可惜的是日本沒有美國那種強制力與大手筆,能開出的條件又猶抱琵琶半遮面,夫人做不到,做妾也不願意,做婢做娼更是蹲不下來,單靠自己恐怕得重新奮鬥30年。

為什麼美國、日本、歐洲都想請台積電去設廠呢?

他們現有的東芝、NEC、日立、飛利浦、摩托羅拉、德儀、三星、英飛凌就不行嗎?

是的! 不行!

因為全世界只有韓國人跟台灣人願意忍受半導體廠那種高壓力又長時間的工作,不論學歷再高也願意嚴守紀律。那些在黃光室都敢偷吃三明治的美國工程師,是不可能做出7奈米的半導體的,更不用說各國都缺乏台灣這種既優秀又願意爆肝,還可以無怨無悔24小時接受傳呼拋家棄子返回工廠加班解決問題的工程師/技術員,願意操作乏味機器的碩士,願意彎腰搬晶片、調化學品的博士。

接下來談談半導體的相關需求

光罩

7奈米製程,完成一組光罩要20億台幣,將來的1/3/5奈米的只會更貴,如果做錯就要再加20億,價錢高到小公司根本無力客製一顆IC,比以前14奈米時代做一組光罩只要2億台幣、28奈米時代做一組光罩只要2000萬元,相差很多倍,早已不是小孩子可以參加的遊戲。

其實不是所有IC都需要7奈米製程

很多汽車零件(車用IC)、消費電子零件、玩具所需要的IC,用28奈米製程來做就綽綽有餘了,如果日本、美國、歐洲這些半導體公司別好高騖遠,願意做14-28奈米製程這是比較正確的,例如聯電早就已經決定不跟風去做7奈米了,還有最近講得沸沸揚揚的力積電也是停留在16-28奈米製程。

基礎建設

台灣已經發展出一套完整的基礎建設與供應鏈,所有半導體生產所需要的化學氣體、液體都是供應商用雙層管路直接送進工廠跟自來水一樣。世界上當前少有任何一個國家能夠做得到,如果想在沙漠裡建立一個半導體工廠,那麼光是所有的化學氣體和液體都要一桶一桶的放在外面,一隻鐵釘一顆螺絲也要空運進來,這樣的廠要順利運轉將會很艱難。

為什麼半導體工廠要建在無人沙漠?因為以前他們歐、美、日自己建的半導體廠,四周的土地、地下水都被污染毒害到寸草不生。這就是為什麼歐洲與美國及日本後來都漸漸放棄在自己國內的土地上生產半導體的真正原因。太陽能電池也是有一樣的問題,所以最後全世界只剩下中國人肯做。

台灣的半導體廠本來也有嚴重污染的問題,後來環保要求越來越嚴格,這些廠商也的確投入了很多錢與努力去做了很多毒物與廢水回收以及高溫毒氣燒毁設備,前幾年日月光的廠區不是就傳出廢水與污染的問題,雖然不能說台灣的這些半導體廠完全解決了汙染問題,但至少跨過了環保門檻,或是應該說台灣這些的半導體公司所投入相關維護環保與符合環境法規的努力真得不落人後甚至是超越國家標準甚多。

水電

半導體生產除了必需耗用大量電力以外,也要使用大量的水,在缺電、缺水的地方是不適合發展的。

周邊

在台灣以外的地區建廠,除了工廠本身以外,其他周邊的協力廠商要全部重建一套,這難度很高。

為什麼台灣的新竹科學園區已經成為全世界最大和最完整的半導體聚落,很少有國家能夠像台灣一樣,任何需要的東西幾乎都可以在2-4小時車程內買得到,在21世紀,地大物博已經不是優點,這讓小而美的台灣在半導體發展上成為最大贏家。

要發展半導體產業沒有個30-40年是根本不可能達到成熟,更不可能會有完整的上下游供應鏈。

問題:

台積電能7->5->3->2奈米製程持續進步的關鍵原因是什麼呢?掌握關鍵技術了嗎?TSMC不是只負責代工生產?那麼製程技術進步又會是什麼原因呢(美方支援或是什麼?)

回覆:

一開始台灣的半導體技術是飛利浦教的,後來是美國TI IBM Motorola 等IC廠回來的那些人才帶回了技術,最近20年是自己研發的,製程進步的目的主是要降低成本,提高速度、減少功耗。

例如製程從14奈米進步到7奈米,速度增加2倍,耗電為1/4 ,同一個12寸晶圓產量變成4倍,每片IC成本降為1/3,就可以用定價將競爭者逼到無利潤邊緣,使其漸漸因龐大的資本支出又沒有利潤而退出市場。以前是三星用這種戰術打敗日本,德國與美國廠,也想勒死台灣的所有IC代工廠,現在是台積電用這種戰術餓死三星也讓韓國的競爭力無法與台積電匹敵。

這篇文章大約是一年前所寫 2021.04.14

分享過來也給各位理財寶的同學們參考

後記: (以上關於半導體的演進與製程技術是一位資深半導體工程師分享)

以下是我個人的一些看法,上面的篇幅內容詳述了整個半導體的演進和相關製程與需求的關鍵,台灣的確有台灣的優勢,這得來不易,但是優勢歸優勢~股價歸股價~還有半導體製程技術有其極限和無法突破的困難點,這絕對不是現在如市場一般人所解讀得什麼先進製程如何又如何,就能為台積電帶來多大的未來成長和貢獻,完全都是信口開河的憑想像!

況且一家公司如台積電這樣每年扛如此龐大的資本支出必須要在未來逐年去做攤提,這對於公司來說未必會是件好事,

相反得公司本身必須要承擔極大的風險!!

以台積電過去10年營收的增長,至去年的整體營收已經超過1.33兆新台幣,去年全年的獲利EPS大約是20元,台積電的股本高達2593億,也就是說台積電去年全年的獲利應該超過5000億新台幣,這非常了不起,但是要期望台積電不斷得繼續擴大增加資本支出,甚至如市場期待要達到300億美金?這如果不是講空話,那就是巴不得台積電倒閉........

台積電獲利營收創新高,一年的資本支出假設維持100億美金就已經沒賺多少錢,如果像這幾年台積電的資本支出已經將近200億美金,那就等於台積電每年近乎是倒貼式的在經營,如果再增加資本支出別說要300億美金了,只要超過200億美金都可能為公司帶來未來營運的風險,加上外資和法人持股似乎都鍾愛於台積電,因為台積電獲利夠穩定,所以一定要高配息.........

那麼請問要馬兒跑又要馬不吃草,台積電要怎麼維持市場與法人期待的高配息股利政策?錢從哪裡來?

就算台積電的毛利60%,營收再成長50%,恐怕都無法滿足市場的期望!

台積電的現金流非常龐大,資本支出很多時候是不得不的選擇,可是一旦台積電的資本支出龐大到足以影響公司的現金流或是整個景氣與需求一旦向下,恐怕對於台積電來說也會是不可承受之重!!

發表

發表

我的網誌

我的網誌